# NEC's LOW POWER GPS RF RECEIVER BIPOLAR ANALOG + INTEGRATED CIRCUIT

# **UPB1009K**

#### **DESCRIPTION**

The  $\mu$ PB1009K is a silicon monolithic IC developed for GPS receivers. This IC integrates a full VCO, second IF filter, 4-bit ADC, and digital control interface to reduce cost and mounting space. In addition, its power consumption is low.

Moreover, use of a TCXO with frequency of 16.368 MHz/16.384 MHz, 14.4 MHz, 19.2 MHz, or 26 MHz switchable with an on-chip divider is possible.

NEC's stringent quality assurance and test procedures ensure the highest reliability and performance.

#### **FEATURES**

Double conversion : fREFin = 16.368 MHz, f1stlFin = 61.380 MHz, f2ndlFin = 4.092 MHz

:  $f_{REFin} = 14.4$ , 16.384, 19.2, 26 MHz,  $f_{1stlFin} = 62.980$  MHz,  $f_{2ndlFin} = 2.556$  MHz

• Multiple system clocks : On-chip switchable frequency divider (1/N = 100, 3/256, 9/1024, 65/4096)

A/D converter

: On-chip 4-bit A/D converter

High-density RF block

: On-chip VCO tank circuit and 2ndIF filter

• Supply voltage : Vcc = 2.7 to 3.3 V

Low current consumption : Icc = 26.0 mA TYP. @ Vcc = 3.0 V, N = 100

High-density surface mountable : 44-pin plastic QFN

#### **APPLICATIONS**

- Consumer use GPS receiver of reference frequency 16.368 MHz, 2nd IF frequency 4.092 MHz

- Consumer use GPS receiver of reference frequency 14.4, 16.384, 19.2, 26 MHz, 2ndIF frequency 2.556 MHz

Caution Observe precautions when handling because these devices are sensitive to electrostatic discharge.

# ORDERING INFORMATION

| Part Number   | Package            | Supplying Form                                                                                                                                        |  |  |

|---------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| μPB1009K-E1-A | 44-pin plastic QFN | <ul> <li>12 mm wide embossed taping</li> <li>Pin 1 indicates pull-out direction of tape</li> <li>Qty 1.5 kpcs/reel, Dry pack specification</li> </ul> |  |  |

**Remark** To order evaluation samples, contact your nearby sales office. Part number for sample order:  $\mu PB1009K$

#### PRODUCT LINE-UP ( $T_A = +25$ °C, $V_{CC} = 3.0 \text{ V}$ )

| Туре                                        | Part Number | Functions<br>(Frequency unit: MHz)                                                                                                                                                              | Vcc<br>(V) | lcc<br>(mA) | CG<br>(dB)    | Package            | Status     |

|---------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|---------------|--------------------|------------|

| Clock<br>Frequency<br>Specific<br>1 chip IC | μΡΒ1009Κ    | Pre-amplifier + RF/IF down-<br>converter + PLL synthesizer<br>REF = 16.368<br>1stIF = 61.380/2ndIF = 4.092<br>REF = 14.4, 16.384, 19.2, 26<br>1stIF = 62.980/2ndIF = 2.556<br>On-chip 4-bit ADC | 2.7 to 3.3 | 26.0        |               | 44-pin plastic QFN | New Device |

|                                             | μΡΒ1008Κ    | LNA + Pre-amplifier + RF/IF<br>down-converter + PLL<br>synthesizer<br>REF = 27.456<br>1stIF = 175.164/2ndIF = 0.132<br>On-chip 2-bit ADC                                                        | 2.7 to 3.3 | 18.0        | 100 to<br>120 | 36-pin plastic QFN |            |

|                                             | μPB1007K    | Pre-amplifier + RF/IF down-<br>converter + PLL synthesizer<br>REF = 16.368<br>1stIF = 61.380/2ndIF = 4.092                                                                                      | 2.7 to 3.3 | 25.0        | 100 to 120    | 36-pin plastic QFN | Available  |

|                                             | μPB1005K    | REF = 16.368<br>1stlF = 61.380/2ndlF = 4.092                                                                                                                                                    |            |             |               | 36-pin plastic QFN |            |

Remark Typical performance. Please refer to ELECTRICAL CHARACTERISTICS in detail.

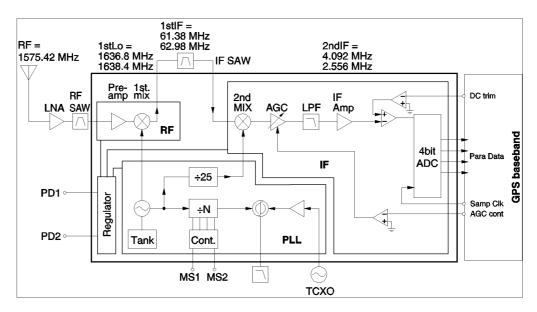

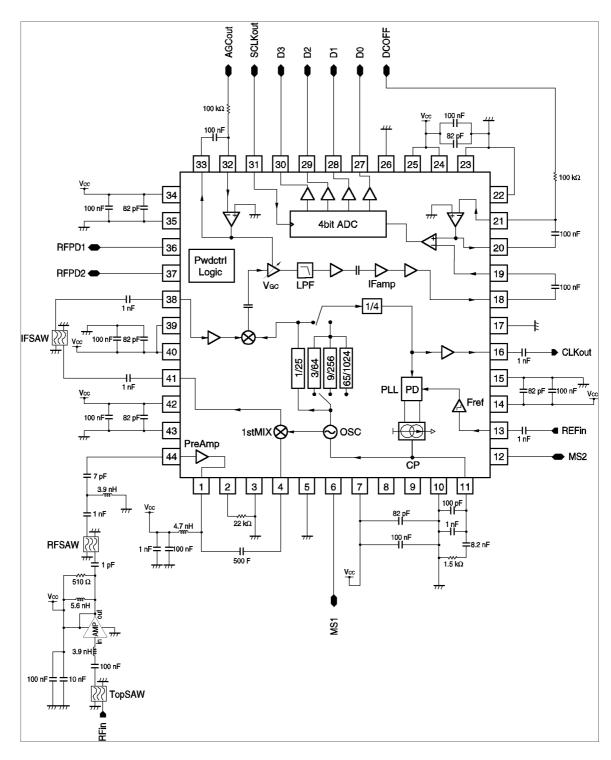

#### SYSTEM APPLICATION EXAMPLE

#### GPS receiver RF block diagram

PD1 and PD2 in the figure are Power Save Mode control pins.

MS1 and MS2 in the figure are TXCO (GPS, W-CDMA, PDC, GSM) control pins.

Caution This diagram schematically shows only the  $\mu PB1009K$ 's internal functions on the system. This diagram does not present the actual application circuits.

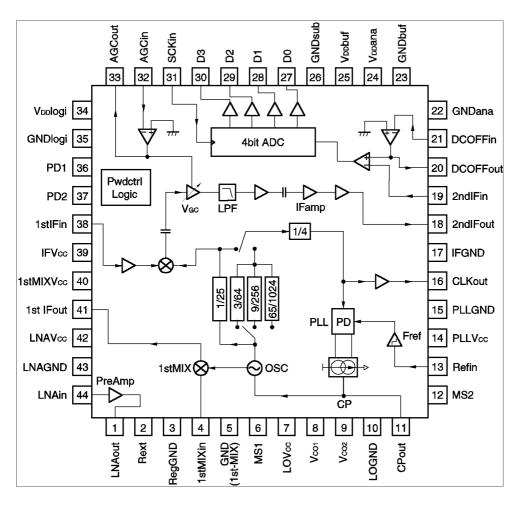

#### PIN CONNECTION AND INTERNAL BLOCK DIAGRAM

# PIN EXPLANATION

| Pin<br>No. | Pin Name  | Function and Application                                                                                                             | Internal Equivalent Circuit |

|------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 1          | PreAMPout | Output pin of preamplifier.                                                                                                          | 1 42                        |

| 2          | Rext      | Connect a resistor for the reference constant-current power supply to this pin. Ground this pin at $22 \ k\Omega$ .                  |                             |

| 3          | RegGND    | Ground pin for regulator.                                                                                                            |                             |

| 42         | PreAmpVcc | Power supply voltage pin for preamplifier. Connect a bypass capacitor to this pin to reduce the high-frequency impedance.            | Regulator Regulator         |

| 43         | PreAmpGND | Ground pin of preamplifier.                                                                                                          |                             |

| 44         | PreAmpin  | Input pin of preamplifier.                                                                                                           | 43 3                        |

| 4          | 1stMIXin  | 1stMIX input pin.                                                                                                                    | 40 + + +                    |

| 5          | 1stMIXGND | Ground pin for first MIX.                                                                                                            |                             |

| 40         | 1stMIXVcc | Power supply voltage pin for RF mixer. Connect a bypass capacitor to this pin to reduce the high-frequency impedance.                | Gibert                      |

| 41         | 1stlFout  | Output pin of RF mixer. Insert an IFSAW filter between this pin and pin 37. The VCO oscillation signal can be monitored on this pin. | Bias                        |

| Pin<br>No. | Pin Name   | Fur                                                                                                             | nction and A       | Application                                                              | Internal Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|------------|-----------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>12    | MS1<br>MS2 | Low: 0 to 0.3 (V)                                                                                               | MS1:L<br>MS2:L     | TCXO : 16.368,<br>16.384 MHz                                             | 14 said                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|            |            | High:<br>Vcc - 0.3 to                                                                                           | MS1 : L<br>MS2 : H | TCXO : 19.2 MHz                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            |            | Vcc (V)                                                                                                         | MS1 : H<br>MS2 : L | TCXO : 14.4 MHz                                                          | 12.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            |            |                                                                                                                 | MS1 : H<br>MS2 : H | TCXO : 26 MHz                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11         | CPout      | R and C to this                                                                                                 | pin to set         | p. Connect external<br>a dumping factor and<br>y (Isink = Isource = 0.45 | 15 S8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13         | Refin      | Reference frequency input pin. Connect an external reference transmitter (such as TCXO) to this pin.            |                    |                                                                          | Bias Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14         | PLLVcc     | Power supply voltage pin of PLL. Connect a bypass capacitor to this pin to reduce the high-frequency impedance. |                    |                                                                          | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15         | PLLGND     | Ground pin of                                                                                                   | PLL.               |                                                                          | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16         | CLKout     | Clock (frexo) o                                                                                                 | utput pin (I       | C test pin).                                                             | Jepinip moujurip mouj |

| Pin<br>No. | Pin Name     | Function and Application                                                                                        | Internal Equivalent Circuit                |

|------------|--------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 7          | LoVcc        | Power supply voltage pin of VCO. Connect a bypass capacitor to this pin to reduce the high-frequency impedance. | VCO                                        |

| 8          | VCO1<br>VCO2 | IC test pin. Leave this pin open when the $\mu$ PB1009K is mounted on board.                                    | 8 VCO cont japinipo                        |

| 10         | LoGND        | Ground pin of VCO.                                                                                              | 10                                         |

| 17         | IFGND        | Ground pin of IF block.                                                                                         | 39 † † † † † † † † † † † † † † † † † † †   |

| 18         | 2ndlFout     | Output pin of IF amplifier.                                                                                     |                                            |

| 38         | 1stlFin      | Input pin of second IF mixer.                                                                                   | 38 18                                      |

| 39         | IFVcc        | Power supply voltage pin of IF block.                                                                           | Bias S S S S S S S S S S S S S S S S S S S |

| Pin<br>No.           | Pin Name             | Function and Application                                                                                                                                                    | Internal Equivalent Circuit |

|----------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 19                   | 2ndlFin              | Input pin of ADC buffer amplifier.                                                                                                                                          | 24                          |

| 20                   | DCOFFout             | Output pin of DC trimming OP amplifier.                                                                                                                                     | 4.7 KD                      |

| 21                   | DCOFFin              | DC trimming pulse input pin. Connect this pin to pin 20 via a capacitor to convert an input pulse signal into DC.                                                           | 19 1.8 kΩ Gy 8 8 9          |

| 22<br>23             | GNDana<br>GNDbuf     | Ground pin for OP amplifier and ADC power supply.                                                                                                                           | 24<br>+                     |

| 24                   | V <sub>DD</sub> ana  | Power supply pin for OP amplifier and ADC comparator.                                                                                                                       | 31                          |

| 25                   | Voobuf               | Power supply pin for output driver amplifier of ADC. Connect this pin to the ground pin of the A/D converter via a bypass capacitor to reduce the high-frequency impedance. | 22 PB                       |

| 26                   | GNDsub               | Ground pin of CMOS substrate.                                                                                                                                               | A Y (27) (29) (28) (30)     |

| 27<br>28<br>29<br>30 | D0<br>D1<br>D2<br>D3 | Digital signal output pins.<br>LSB = D0, MSB = D3                                                                                                                           |                             |

| 31                   | SCKin                | Sampling clock signal input pin.                                                                                                                                            | 23 (24)                     |

| 32                   | AGCin                | AGC control pulse signal input pin.                                                                                                                                         |                             |

| 33                   | AGCout               | AGC control signal output pin.                                                                                                                                              | 21 20 33 33                 |

| Pin<br>No. | Pin Name   | Function and Application                          |                    |                                        | Internal Equivalent Circuit |

|------------|------------|---------------------------------------------------|--------------------|----------------------------------------|-----------------------------|

| 34         | Vdologi    | Power supply voltage pin for power control logic. |                    |                                        | 34                          |

| 35         | GNDlogi    | Ground pin for                                    | power cor          | ntrol logic.                           |                             |

| 36<br>37   | PD1<br>PD2 | Low: 0 to 0.3 (V)                                 | PD1 : L<br>PD2 : L | Sleep mode (all circuits off).         | 36                          |

|            |            |                                                   | PD1 : L<br>PD2 : H | Warm-up mode (PLL on).                 | 37                          |

|            |            |                                                   | PD1 : H<br>PD2 : L | Calibration mode (PLL + IF + AD C on). |                             |

|            |            |                                                   | PD1 : H<br>PD2 : H | Active mode (all circuits on).         | 35                          |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                     | Symbol           | Test Conditions           | Ratings     | Unit |

|-------------------------------|------------------|---------------------------|-------------|------|

| Supply Voltage                | Vcc              | T <sub>A</sub> = +25°C    | 3.6         | V    |

| Total Circuit Current         | <b>I</b> CCTotal | T <sub>A</sub> = +25°C    | 100         | mA   |

| Power Dissipation             | P□               | $T_A = +25^{\circ}C$ Note | 266         | mW   |

| Operating Ambient Temperature | TA               |                           | -40 to +85  | °C   |

| Storage Temperature           | T <sub>stg</sub> |                           | -55 to +125 | °C   |

Note Mounted on double-sided copper-clad 50  $\times$  50  $\times$  1.6 mm epoxy glass PWB

## RECOMMENDED OPERATING RANGE

| Parameter                                  | Symbol               | MIN.      | TYP.            | MAX. | Unit |

|--------------------------------------------|----------------------|-----------|-----------------|------|------|

| Supply Voltage                             | Vcc                  | 2.7       | 3.0             | 3.3  | V    |

| Operating Ambient Temperature              | TA                   | -30       | +25             | +85  | °C   |

| RF Input Frequency                         | <b>f</b> RFin        | -         | 1 575.42        | -    | MHz  |

| 1st LO Oscillating Frequency               | f <sub>1stLOin</sub> | -         | 1 636.8/1 638.4 | -    | MHz  |

| 1st IF Input Frequency                     | f <sub>1stlFin</sub> | -         | 61.38/62.98     | -    | MHz  |

| 2nd LO Input Frequency                     | <b>f</b> 2ndLOin     | -         | 65.472/65.536   | -    | MHz  |

| 2nd IF Input Frequency                     | <b>f</b> 2ndlFin     | -         | 4.092/2.556     | -    | MHz  |

| Reference Input/Output Frequency           | fREFin<br>fREFout    | -         | TCXO            | -    | MHz  |

| Clock mode control voltage<br>(Low Level)  | V <sub>IL1</sub>     | 0         | -               | 0.3  | V    |

| Clock mode control voltage<br>(High Level) | V <sub>IH1</sub>     | Vcc - 0.3 | -               | Vcc  | V    |

| Power-down control voltage<br>(Low Level)  | V <sub>IL2</sub>     | 0         | -               | 0.3  | V    |

| Power-down control voltage<br>(High Level) | V <sub>IH2</sub>     | Vcc - 0.3 | -               | Vcc  | V    |

#### POWER-DOWN CONTROL MODE

The  $\mu$ PB1009K consists of an RF block, an IF block, and a PLL block. By controlling reduction of power to each block (by applying a voltage to the PD1 and PD2 pins), the following four modes can be used.

| Mode | Mode Name        | Test Conditions |   | RF Block | IF Block   | PLL Block |

|------|------------------|-----------------|---|----------|------------|-----------|

| No.  |                  | PD1 PD2         |   |          | (IF + ADC) |           |

| 1    | Active mode      | L               | Н | ON       | ON         | ON        |

| 2    | Calibration mode | Н               | Н | OFF      | ON         | ON        |

| 3    | Warm-up mode     | Н               | L | OFF      | OFF        | ON        |

| 4    | Sleep mode       | L               | L | OFF      | OFF        | OFF       |

Caution To use only the active mode and sleep mode, fix PD1 to L and select the desired mode with PD2.

#### REFERENCE CLOCK CONTROL MODE

The divided frequency can be selected as follows so that it can be shared with the TCXO of each system.

| TCXO Frequency                       | Test Conditions |     | 1/N     | Phase Comparison Frequency |

|--------------------------------------|-----------------|-----|---------|----------------------------|

|                                      | PD1             | PD2 |         |                            |

| 16.368 MHz (GPS)<br>16.384 MHz (GPS) | L               | L   | 1/100   | 16.368 MHz<br>16.384 MHz   |

| 19.2 MHz (W-CDMA)                    | L               | Н   | 3/256   | 19.2 MHz                   |

| 14.4 MHz (PDC)                       | Н               | L   | 9/1024  | 14.4 MHz                   |

| 26 MHz (GSM)                         | Н               | Н   | 65/4096 | 26 MHz                     |

Caution When the reference clock frequency is 16.368 MHz, the 1stIF frequency and 2ndIF frequency are 61.38 MHz and 4.092 MHz, respectively. They are respectively 62.98 MHz and 2.556 MHz in all other cases.

# ELECTRICAL CHARACTERISTICS (TA = +25°C, Vcc = 3.0 V)

| Parameter                                    | Symbol                    | Test Conditions                                                                               | MIN.       | TYP.             | MAX.       | Unit    |

|----------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------|------------|------------------|------------|---------|

| Rest current of overall IC in each mode      | Rest status<br>MS1 = L, M | s without input signal, including sampling clock<br>/IS2 = L                                  | ζ.         |                  |            |         |

| Sleep mode Note                              | Is                        | PD1 = L, PD2 = L                                                                              | 1.3        | 2.2              | 3.5        | mA      |

| Warm-up mode                                 | lw                        | PD1 = H, PD2 = L                                                                              | 10.5       | 13.0             | 15.5       | mA      |

| Calibration mode                             | lc                        | PD1 = H, PD2 = H                                                                              | 18.0       | 22.0             | 25.3       | mA      |

| Active mode                                  | la                        | PD1 = L, PD2 = H                                                                              | 22.1       | 26.0             | 30.0       | mA      |

| Rest current of PLL block in each clock mode |                           | PLL block. Overall current in calibration mode $\Theta$ (MS1 = L, MS2 = L). PD1 = H, PD2 = L. | and active | e mode incr      | eases from | that in |

| Current when 1/100 divider is used           | lw1                       | MS1 = L, MS2 = L                                                                              | 5.3        | 6.5              | 7.6        | mA      |

| Current when 256/3 divider is used           | lw2                       | MS1 = L, MS2 = H                                                                              | 9.7        | 11.3             | 12.6       | mA      |

| Current when 1024/9 divider is used          | lwз                       | MS1 = H, MS2 = L                                                                              | 10.2       | 12.1             | 13.5       | mA      |

| Current when 4096/65 divider is used         | lw4                       | MS1 = H, MS2 = H                                                                              | 10.4       | 12.3             | 13.9       | mA      |

| Maximum mode control pin current             |                           |                                                                                               |            |                  |            |         |

| 6 pin                                        | MS1                       | H application                                                                                 | -          | -                | 20         | μΑ      |

|                                              |                           | L application                                                                                 | -20        | -                | -          | μΑ      |

| 12 pin                                       | MS2                       | H application                                                                                 | Ī          | ī                | 20         | μΑ      |

|                                              |                           | L application                                                                                 | -20        | -                | -          | μΑ      |

| 36 pin                                       | PD1                       | H application                                                                                 | 1          | -                | 1          | μΑ      |

|                                              |                           | L application                                                                                 | -1         | -                | _          | μΑ      |

| 37 pin                                       | PD2                       | H application                                                                                 | -          | -                | 1          | μΑ      |

|                                              |                           | L application                                                                                 | -1         | -                | 1          | μΑ      |

| <pre-amplifier></pre-amplifier>              | frFin = 1 57              | 5.42 MHz                                                                                      |            |                  |            |         |

| Circuit Current 1                            | Icc1                      | No Signals, 1-pin current                                                                     | 1.9        | 2.3              | 2.7        | mA      |

| Power Gain                                   | GLNA                      | $P_{RFin} = -40 \text{ dBm}$                                                                  | 12.5       | 15.0             | 17.5       | dB      |

| Noise Figure                                 | NFLNA                     | f <sub>RFin</sub> = 1 575 MHz                                                                 | -          | 3.0              | 3.5        | dB      |

| Saturated Output Power                       | Po(SAT)LNA                | P <sub>RFin</sub> = -10 dBm                                                                   | -4.0       | -2.7             | -          | dBm     |

| Input 1dB Compression Level                  | P <sub>LNA-1</sub>        | frFin = 1 575.42 MHz                                                                          | -25        | -21.8            | _          | dBm     |

| Input 3rd Order Intercept Point              | IIP3LNA                   | frFin = 1 575.42 MHz, 1 576.42 MHz                                                            | -12        | -9.5             | Ī          | dBm     |

| Input Inpedance                              | ZinLNA                    | Calculated from S-parameter where input DC cut capacitance = 1 nF, output load L =            | ı          | 11.2 –<br>j21.5  | ı          | Ω       |

| Output Inpedance                             | ZoutLNA                   | 100 n, and DC cut capacitance = 1 nF                                                          | -          | 16.4 –<br>j136.6 | ı          | Ω       |

**Note** Most of the current flows into the ADC ladder resistor (V<sub>DD</sub>ana ◆ GNDana) in the sleep mode, and the sleep mode current between other V<sub>CC</sub> (V<sub>DD</sub>) and GND is 10  $\mu$ A maximum.

# ELECTRICAL CHARACTERISTICS (TA = +25°C, Vcc = 3.0 V)

| Parameter                            | Symbol                  | Test Conditions                                                                                          |                                       | MIN.  | TYP.            | MAX. | Unit     |

|--------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------|-------|-----------------|------|----------|

| <rf mixer=""></rf>                   | f <sub>RF</sub> = 1 575 | 5.42 MHz, f1stLOin = 1 63                                                                                | 36.80 MHz, f <sub>1stlF</sub> = 61.38 | MHz   |                 |      |          |

| Circuit Current 2                    | Icc2                    | No Signals, 40 pin current                                                                               |                                       | 2.0   | 2.5             | 3.0  | mA       |

| RF Conversion Gain                   | CGRF                    | Premixin = -40 dBm                                                                                       |                                       | 14.0  | 16.1            | 19.0 | dB       |

| Noise Figure                         | S SBN Fr fm ix          | SSBNF = 10*log (2*I<br>-1) MHz                                                                           | OSBNF (Linear value)                  | -     | 12.8            | 16.0 | dB       |

| Maximum IF Output                    | Po (SAT) REMIX          | Premixin = -10 dBm                                                                                       |                                       | -4.0  | -0.8            | -    | dBm      |

| Input 1dB Compression Level          | P <sub>RFMIX-1</sub>    | fremixin = 1 575.42 MH                                                                                   | łz                                    | -29.0 | -25.5           | -    | dBm      |

| Input 3rd Order Intercept Point      | IIP3RFMIX               | fremixin = 1 575.42 MH<br>f1stLO = 1 636.8 MHz                                                           | lz, 1 576.42 MHz                      | -19.0 | -17.2           | 1    | dBm      |

| LO Leakage to IF Pin                 | LOF                     | Leakage of 1 636.8 M                                                                                     |                                       | ı     | -34.5           | -30  | dBm      |

| LO Leakage to RF Pin                 | LORF                    | VCO oscillates corre                                                                                     | ctly.                                 | Ī     | -54.7           | -30  | dBm      |

| Input Inpedance                      | ZinMIX                  | Calculated from S-pa DC cut capacitance =                                                                | ·                                     | 1     | 50.1 –<br>j22.3 | 1    | Ω        |

| Output Inpedance                     | ZoutMIX                 | cut capacitance = 1 nF                                                                                   |                                       | -     | 57.3 +<br>j2.6  | -    | Ω        |

| <if ifamp="" lpf,="" mixer,=""></if> | $f_{1stFin} = 61.3$     | 38 MHz, f <sub>2ndLOin</sub> = 65.4                                                                      | 72 MHz, Z∟ = 2 kΩ                     |       |                 |      |          |

| Circuit Current 3                    | Іссз                    | No Signals, 39 pin cu                                                                                    | rrent                                 | 6.3   | 7.3             | 8.5  | mA       |

| IF Conversion Gain                   | CG (GV) IF              | Vagc = 0.5 V                                                                                             |                                       | 66.0  | 70.3            | 75.0 | dB       |

|                                      |                         | Vagc = 1.5 V                                                                                             | V <sub>AGC</sub> = 1.5 V              |       | 51.2            | 58.0 | dB       |

|                                      |                         | V <sub>AGC</sub> = 2.5 V                                                                                 |                                       | 19.5  | 26.4            | 33.5 | dB       |

| In Band Gain Fluctuation             | ∆CG1                    | 3.092 to 5.092 MHz                                                                                       |                                       | ı     | 0.7             | 1.0  | dB       |

| Out Of Band Attenuation              | ∆CG2                    | Gain difference at 4.0 MHz, Vagc = 0.5 V                                                                 | 92 MHz and 9.092                      | 20.0  | 25.0            | -    | dB       |

| Conversion Gain Range                | CGRange                 | V <sub>AGC</sub> = 0 to 2.5 V                                                                            |                                       | 32.5  | 43.9            | -    | dB       |

| IF · SSB Noise Figure                | NFıF                    | V <sub>AGC</sub> = 0.5 V (at max                                                                         | imum gain)                            | -     | 13.7            | 17.5 | dB       |

| Maximum 2ndIF Output                 | Vo (SAT) F              | Pin = -50 dBm, Vago :                                                                                    | = 0.5 V                               | 1.0   | 1.3             | 1    | $V_{PP}$ |

| Input 1dB Compression Level          | P <sub>IF-1</sub>       | f <sub>1stlFin</sub> = 61.38 MHz                                                                         | Vagc = 0.5 V                          | -70.5 | -64.4           | ı    | dBm      |

|                                      |                         |                                                                                                          | Vagc = 1.5 V                          | -53.5 | -44.9           | ı    | dBm      |

|                                      |                         | V <sub>AGC</sub> = 2.5 V                                                                                 |                                       | -37.0 | -30.6           | Ī    | dBm      |

| Input 3rd Order Intercept Point      | IIРзг                   | f <sub>1stlFin1</sub> = 61.28 MHz                                                                        | Vagc = 0.5 V                          | -56.0 | -51.3           | -    | dBm      |

|                                      |                         | f1stlFin2 = 61.38 MHz                                                                                    | Vagc = 1.5 V                          | -38.0 | -30.7           | -    | dBm      |

|                                      |                         | f <sub>2ndLO</sub> = 65.472 MHz V <sub>AGC</sub> = 2.5 V                                                 |                                       | -27.0 | -21.4           | -    | dBm      |

| Input Inpedance                      | ZinIF                   | Calculated from S-parameter where input DC cut capacitance = 1 nF and output DC cut capacitance = 100 nF |                                       | -     | 69.3 –<br>j4.8  | 1    | Ω        |

| Output Inpedance                     | ZoutIF                  |                                                                                                          |                                       | -     | 163 +<br>j3.8   | -    | Ω        |

# ELECTRICAL CHARACTERISTICS (TA = +25°C, Vcc = 3.0 V)

| Parameter                          | Symbol      | Test Conditions                                                                         | MIN.    | TYP.  | MAX.  | Unit        |

|------------------------------------|-------------|-----------------------------------------------------------------------------------------|---------|-------|-------|-------------|

| <pll synthesizer=""></pll>         |             |                                                                                         |         |       |       |             |

| Circuit Current 4                  | Icc4        | PLL, VCO current, MS1 = L, MS2 = L                                                      | 8.0     | 9.5   | 10.6  | mA          |

| Charge Pump Output Current         | Icpsink     | V <sub>13 pin</sub> = V <sub>CC</sub> /2                                                | -0.55   | -0.45 | -0.35 | mA          |

|                                    | Icpsource   |                                                                                         | 0.35    | 0.45  | 0.55  | mA          |

| Loop Filer Output (High Level)     | <b>V</b> oн |                                                                                         | Vcc-0.3 | 1     | -     | V           |

| Loop Filer Output (Low Level)      | Vol         |                                                                                         | _       | ı     | 0.2   | V           |

| Reference Input Level              | VREFin      |                                                                                         | _       | 0.2   | 1.6   | <b>V</b> PP |

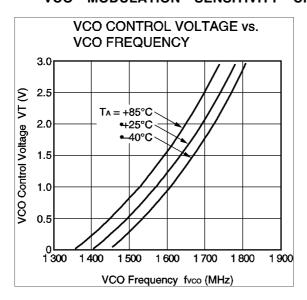

| VCO Modulation Sensitivity         | KV          | Center frequency                                                                        | _       | 100   | ı     | MHz         |

| VCO Control Voltage                | VT          | When PLL is Locked                                                                      | 0.5     | 1.3   | 2.0   | V           |

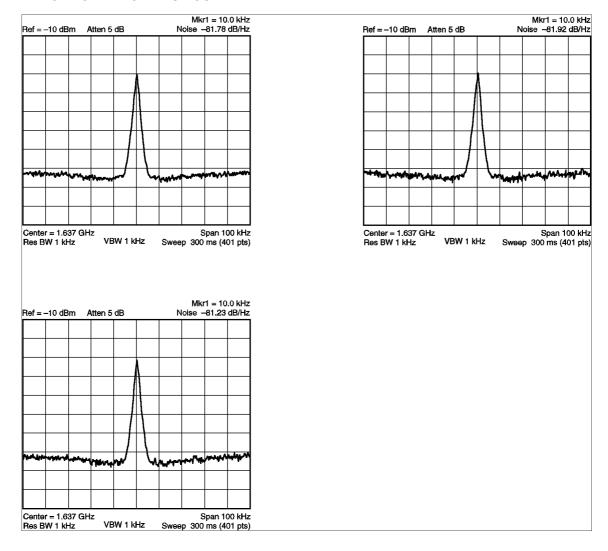

| C/N                                | C/N         | ∆10 kHz                                                                                 | 70.0    | 81.0  | -     | dBc/Hz      |

| <a converter="" d=""></a>          |             |                                                                                         |         |       |       |             |

| Circuit Current 5                  | Icc5        |                                                                                         | 3.1     | 4.1   | 5.4   | mA          |

| Resolution                         | ResAD       |                                                                                         | _       | 4     | ı     | bits        |

| Sampling Clock                     | fs          |                                                                                         | _       | ı     | 20    | MHz         |

| Input Band Width                   | ADBW        |                                                                                         | 5.1     | ı     | ı     | MHz         |

| Integral Non-linear Error          | INL         | DC characteristics                                                                      | _       | 0.2   | 1.0   | LSB         |

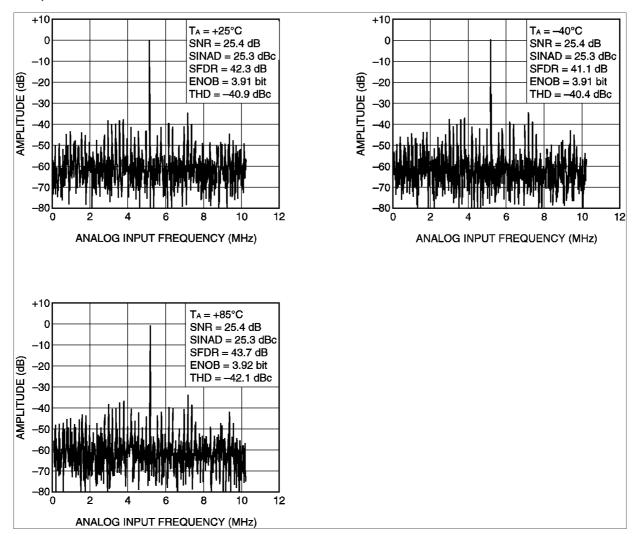

| Signal-to-noise Ratio              | SNR         | IF = 5.17 MHz, fs = 20.48 MHz                                                           | 22.0    | 25.3  | ı     | dB          |

| Signal-to-noise + Distortion Ratio | SINAD       | IF = 5.17 MHz, fs = 20.48 MHz                                                           | 20.0    | 25.1  | -     | dB          |

| Number                             | ENOB        | ENOB = (SINAD-1.763)/6.02                                                               | 3.0     | 3.9   | -     | bits        |

| Total Harmonic Distortion Ratio    | THD         | IF = 5.17 MHz, fs = 20.48 MHz<br>Second-degree to fifth-degree distortion<br>components | -       | -40   | -30   | dBc         |

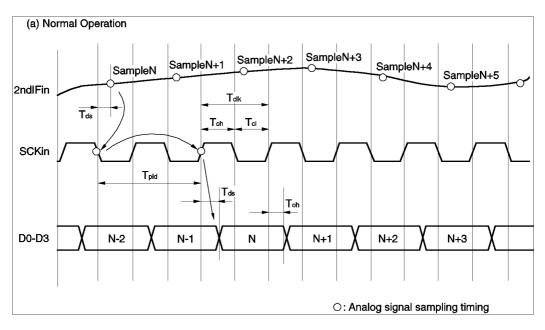

#### Remarks 1. Timing characteristics of ADC during normal operation

A buffer amplifier is internally inserted before the ADC core of the  $\mu$ PB1009K. The bias of this buffer amplifier is controlled by the signal input from the DC trim pin, and is used to eliminate the DC offset of the ADC. Because the ladder resistor of the ADC is directly connected between VDDana and GNDana, changes in VDDana affect the resolution of the ADC.

As illustrated in the operation timing chart below, the data of SampleN is pipeline delayed by 1.5 clocks during normal operation, and is output at the rising edge of the sample clock with output delay time Tod. When the operation is changed from normal operation to power-down operation, the status of the output data immediately before the power-down operation is retained (drive status).

The following table shows each timing parameter for reference purposes.

| Symbol           | Parameter                          | Test Conditions                                     | MIN. | TYP. | MAX. | Unit  |

|------------------|------------------------------------|-----------------------------------------------------|------|------|------|-------|

| Tod              | Output Delay                       | C <sub>L</sub> = 10 pF, f <sub>clk</sub> = 19.2 MHz | 1    | 1    | 12   | ns    |

| T <sub>pld</sub> | Pipeline Delay                     |                                                     | 1    | 1.5  | 1    | clock |

| Tds              | Sampling Delay<br>(Aperture Delay) |                                                     | ı    | 2    | ı    | ns    |

| Toh              | Output Hold Time                   |                                                     | 2    | -    | _    | ns    |

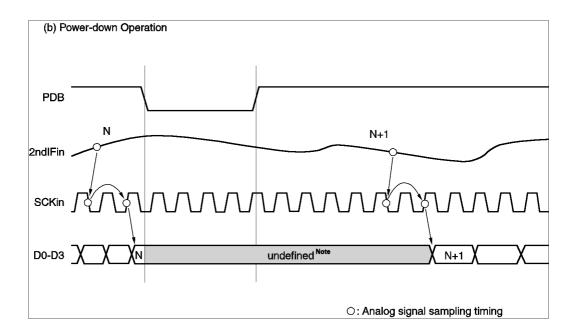

## Remarks 2. Power-down timing characteristics of ADC

The output code of the ADC of the  $\mu$ PB1009K is undefined for 7.5 clocks after the power-down signal is cleared when the ADC returns from the power-down status to normal operation.

**Note** The output data is undefined from the start of the power-down operation to the 7.5th clock from the falling edge of the clock at which the power-down operation is cleared.

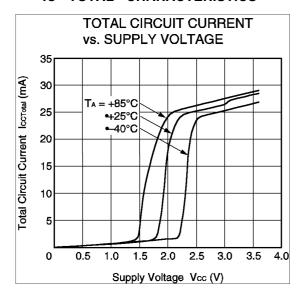

# TYPICAL CHARACTERISTICS (TA = +25°C, Vcc = 3.0 V, unless otherwise specified) — IC TOTAL CHARACTERISTICS —

**Remark** The graphs indicate nominal characteristics.

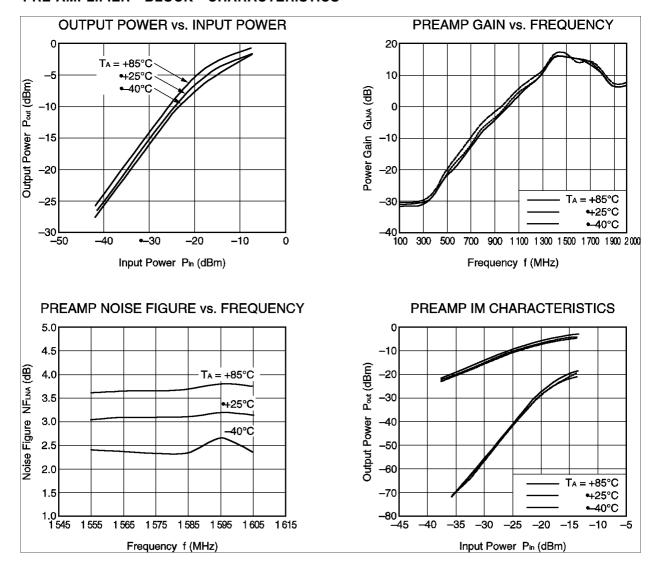

# — PRE-AMPLIFIER BLOCK CHARACTERISTICS —

Remark The graphs indicate nominal characteristics.

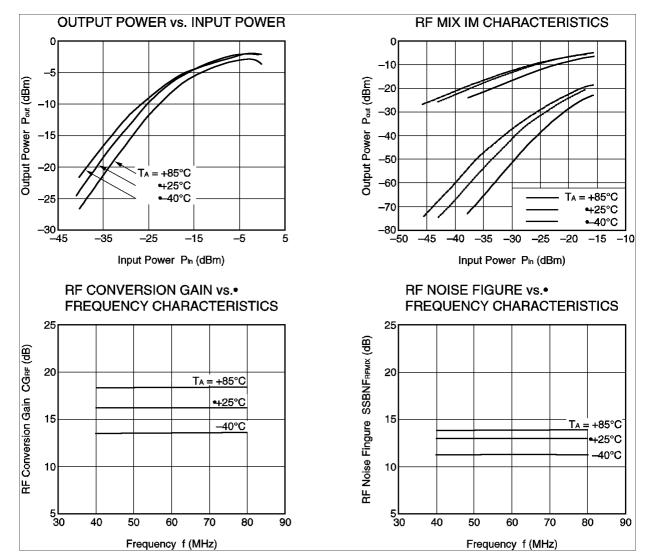

#### - RF MIX BLOCK CHARACTERISTICS -

Remark The graphs indicate nominal characteristics.

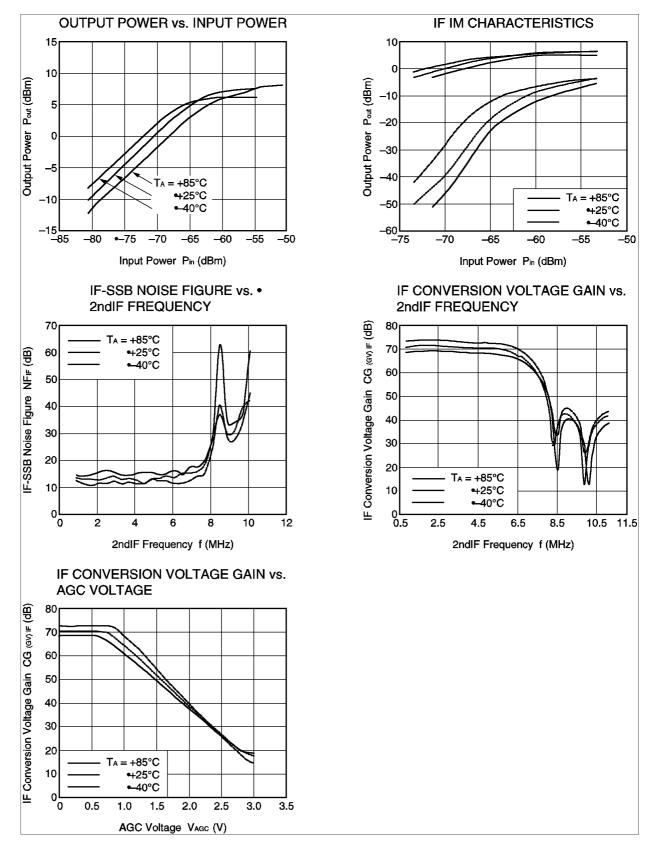

#### — IF BLOCK CHARACTERISTICS —

Remark The graphs indicate nominal characteristics.

# - VCO MODULATION SENSITIVITY CHARACTERISTICS -

#### — C/N CHARACTERISTICS —

Remark The graphs indicate nominal characteristics.

# — SINAD CHARACTERISTICS OF A/D CONVERTOR (IFin = $5.17~\mathrm{MHz}$ , SCLKin = $20.48~\mathrm{MHz}$ ) —

Remark The graphs indicate nominal characteristics.

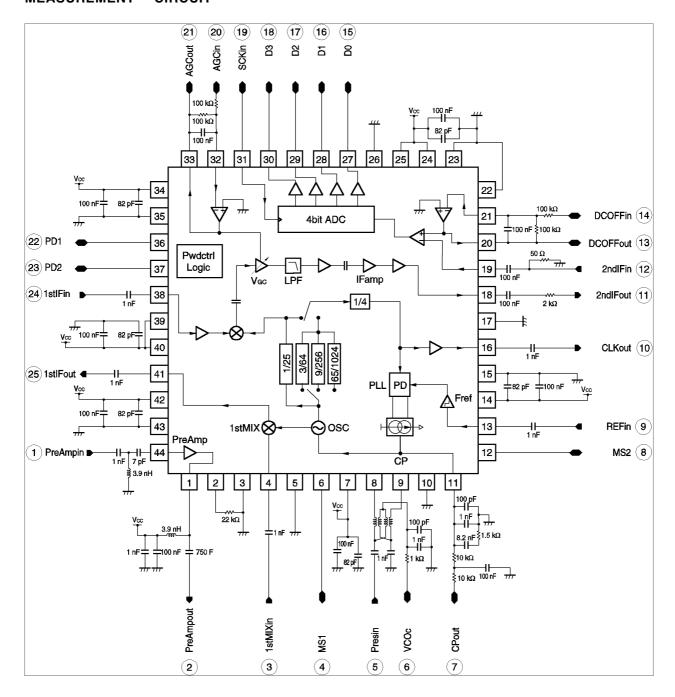

#### MEASUREMENT CIRCUIT

# DESCRIPTION OF PINS OF TEST CIRCUIT

| Pin No. | Pin Function                            | Pin Name  | Pin No. | Pin Function                        | Pin Name |

|---------|-----------------------------------------|-----------|---------|-------------------------------------|----------|

| 1       | Preamplifier Input                      | PreAmpin  | (14)    | DC Offset Input                     | DCOFFin  |

| 2       | Preamplifier Output                     | PreAmpout | 15      | Digital Signal Output Pin           | D0       |

| 3       | RF Mixer Input                          | 1stMIXin  | 16      |                                     | D1       |

| 4       | MS1                                     | MS1       | 17)     |                                     | D2       |

| 5       | Prescaler Input                         | Presin    | 18      |                                     | D3       |

| 6       | VCO Power Control Pin                   | VCOc      | 9       | Sampling Signal Input               | SCKin    |

| 7       | VT Measurement Pin (Charge Pump Output) | CPout     | 20      | AGC Input                           | AGCin    |

| 8       | MS2                                     | MS2       | 21      | AGC Control Voltage Output          | AGCout   |

| 9       | Reference Clock Input                   | REFin     | 2       | PD1 Output (Default onboard : GND)  | PD1      |

| 10      | Clock Output                            | CLKout    | 23      | PD1 Output (Default on board : Vcc) | PD2      |

| 11)     | 2ndIF Output                            | 2ndlFout  | 24      | 1stIF Input                         | 1stlFin  |

| 12      | 2ndIF Input                             | 2ndlFin   | 25      | 1stIF Output                        | 1stlFout |

| 13      | DC Offset Output                        | DCOFFout  |         |                                     |          |

#### **APPLICATION CIRCUIT**

| PD1 | PD2 | Power-down mode           |  |

|-----|-----|---------------------------|--|

| 0   | 0   | Sleep mode (full off)     |  |

| 1   | 0   | Warm-up mode (PLL on)     |  |

| 1   | 1   | Calibration mode (PLL on) |  |

| 0   | 1   | Active mode (full on)     |  |

| MS1 | MS2 | TCXO              | N       |

|-----|-----|-------------------|---------|

| 0   | 0   | 16.368/16.384 MHz | 100     |

| 0   | 1   | 19.2 MHz          | 256/3   |

| 1   | 0   | 14.4 MHz          | 1024/9  |

| 1   | 1   | 26.0 MHz          | 4096/65 |

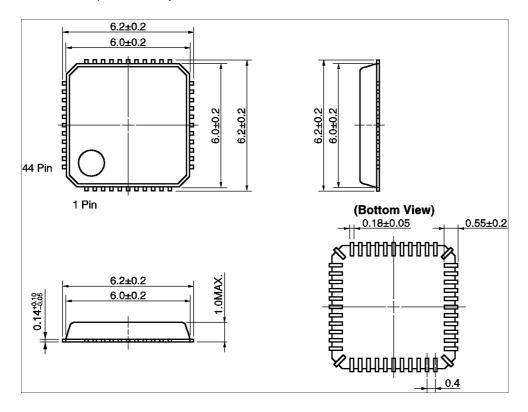

#### PACKAGE DIMENSIONS

## 44-PIN PLASTIC QFN (UNIT: mm)

Caution The island pins located on the corners are needed to fabricate products in our plant, but do not serve any other function. Consequently the island pins should not be soldered and should remain non-connection pins.

#### NOTES ON CORRECT USE

- (1) Observe precautions for handling because of electro-static sensitive devices.

- (2) Form a ground pattern as widely as possible to minimize ground impedance (to prevent abnormal oscillation).

- (3) Keep the wiring length of the ground pins as short as possible.

- (4) Connect a bypass capacitor to the Vcc pin.

- (5) High-frequency signal I/O pins must be coupled with the external circuit using a coupling capacitor.

#### RECOMMENDED SOLDERING CONDITIONS

This product should be soldered and mounted under the following recommended conditions. For soldering methods and conditions other than those recommended below, contact your nearby sales office.

| Soldering Method | Soldering Conditions                                                                                                                                                                                                              |                                                                                                                           | Condition Symbol |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------|

| Infrared Reflow  | Peak temperature (package surface temperature) Time at peak temperature Time at temperature of 220°C or higher Preheating time at 120 to 180°C Maximum number of reflow processes Maximum chlorine content of rosin flux (% mass) | : 260°C or below<br>: 10 seconds or less<br>: 60 seconds or less<br>: 120±30 seconds<br>: 3 times<br>: 0.2%(Wt.) or below | IR260            |

| VPS              | Peak temperature (package surface temperature) Time at temperature of 200°C or higher Preheating time at 120 to 150°C Maximum number of reflow processes Maximum chlorine content of rosin flux (% mass)                          | : 215°C or below<br>: 25 to 40 seconds<br>: 30 to 60 seconds<br>: 3 times<br>: 0.2%(Wt.) or below                         | VP215            |

| Wave Soldering   | Peak temperature (molten solder temperature) Time at peak temperature Preheating temperature (package surface temperature) Maximum number of flow processes Maximum chlorine content of rosin flux (% mass)                       | : 260°C or below<br>: 10 seconds or less<br>: 120°C or below<br>: 1 time<br>: 0.2%(Wt.) or below                          | WS260            |

| Partial Heating  | Peak temperature (pin temperature) Soldering time (per side of device) Maximum chlorine content of rosin flux (% mass)                                                                                                            | : 350°C or below<br>: 3 seconds or less<br>: 0.2%(Wt.) or below                                                           | HS350            |

Caution Do not use different soldering methods together (except for partial heating).

Life Support Applications

These NEC products are not intended for use in life support devices, appliances, or systems where the malfunction of these products can reasonably be expected to result in personal injury. The oustomers of CEL using or selling these products for use in such applications do so at their own risk and agree to fully indomnity CEL for all damages resulting from such improper use or sale.

| MORE California Eastern Laboratories, Your source for NEC RF, Microwave, Optoelectronic, and Fiber Optic Semiconductor Devices. 4550 Parist Henry Drive - Sents Clark, CA 95054-1817 - (408) 958-3500 - FAX (408) 988-3229 - www.sel.com

DATA SUBJECT TO CHANGE WITHOUT NOTICE

12.04.0008

4590 Patrick Henry Drive Santa Clara, CA 95054-1817 Telephone: (408) 919-2500

Facsimile: (408) 988-0279

Subject: Compliance with EU Directives

CEL certifies, to its knowledge, that semiconductor and laser products detailed below are compliant with the requirements of European Union (EU) Directive 2002/95/EC Restriction on Use of Hazardous Substances in electrical and electronic equipment (RoHS) and the requirements of EU Directive 2003/11/EC Restriction on Penta and Octa BDE.

CEL Pb-free products have the same base part number with a suffix added. The suffix –A indicates that the device is Pb-free. The –AZ suffix is used to designate devices containing Pb which are exempted from the requirement of RoHS directive (\*). In all cases the devices have Pb-free terminals. All devices with these suffixes meet the requirements of the RoHS directive.

This status is based on CEL's understanding of the EU Directives and knowledge of the materials that go into its products as of the date of disclosure of this information.

| Restricted Substance per RoHS | Concentration Limit per RoHS (values are not yet fixed) | Concentration in CEL | on contained<br>devices |  |

|-------------------------------|---------------------------------------------------------|----------------------|-------------------------|--|

| Lead (Pb)                     | < 1000 PPM                                              | -A<br>Not Detected   | -AZ<br>(*)              |  |

| Mercury                       | < 1000 PPM                                              | Not Detected         |                         |  |

| Cadmium                       | < 100 PPM                                               | Not Detected         |                         |  |

| Hexavalent Chromium           | < 1000 PPM                                              | Not Detected         |                         |  |

| PBB                           | < 1000 PPM                                              | Not Detected         |                         |  |

| PBDE                          | < 1000 PPM                                              | Not Detected         |                         |  |

If you should have any additional questions regarding our devices and compliance to environmental standards, please do not hesitate to contact your local representative.

Important Information and Disclaimer: Information provided by CEL on its website or in other communications concerting the substance content of its products represents knowledge and belief as of the date that it is provided. CEL bases its knowledge and belief on information provided by third parties and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. CEL has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. CEL and CEL suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall CEL's liability arising out of such information exceed the total purchase price of the CEL part(s) at issue sold by CEL to customer on an annual basis.

See CEL Terms and Conditions for additional clarification of warranties and liability.